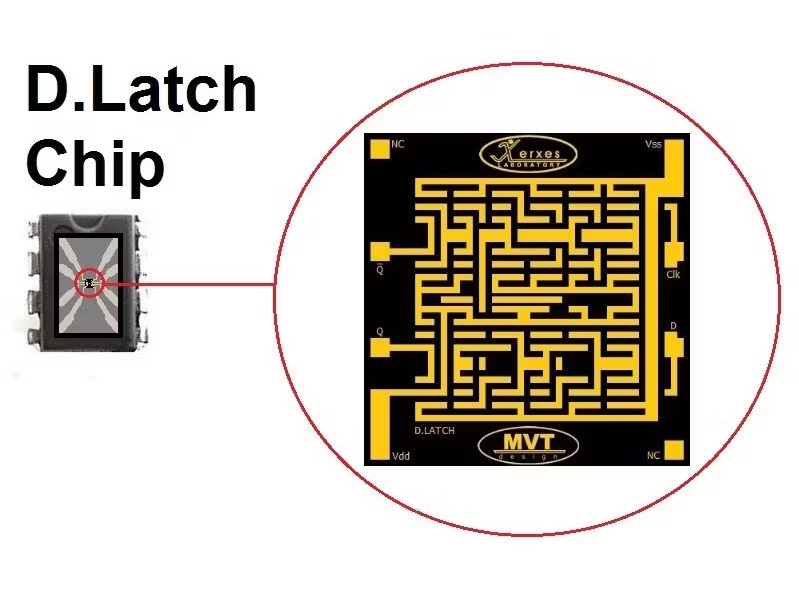

D-Latch-Flip-Flop-Chip-Design

Ein D-Latch-Flip-Flop ist tatsächlich ein Ein-Bit-Random Access Memory (RAM). Das bedeutet, dass der „Q“-Pin beim Start „1“ oder „0“ sein kann. Durch die Parallelschaltung von 8 D.-Latches können Sie einen 8-Bit- oder 1-Byte-RAM erstellen.

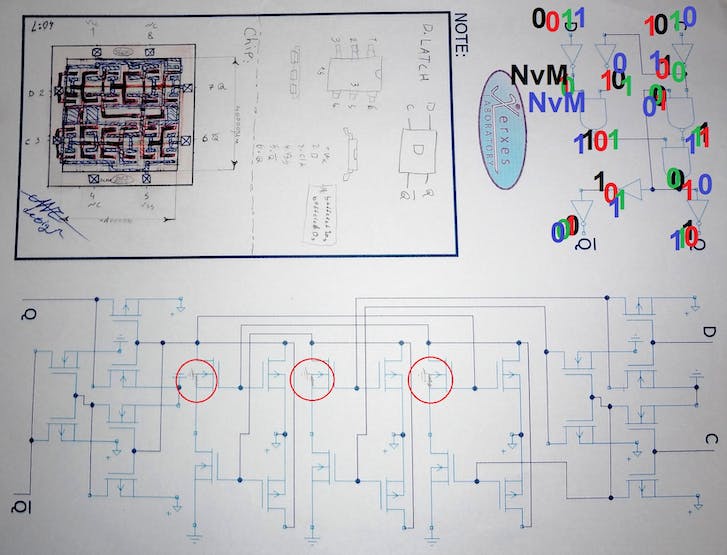

Der D-Riegel, den ich auf Papier entworfen habe, unterscheidet sich ein wenig von den üblichen Schaltplänen. Als ich es entwarf, war ich erst 20 Jahre alt und habe es entworfen, indem ich einige Artikel über digitale Gatter und das Design integrierter Schaltkreise gelesen habe.

***““Elektronik-, Programmier- und Arduino-Projekte, einschließlich Quellcodes, Schaltpläne und PCB-Pläne für Ingenieure, Studenten und Bastler““***

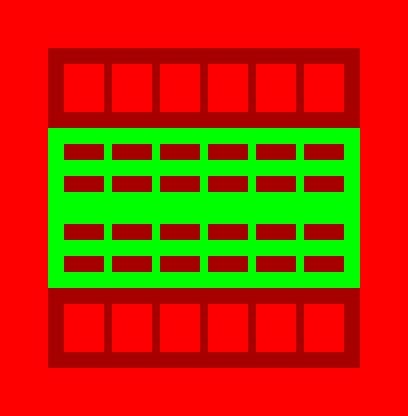

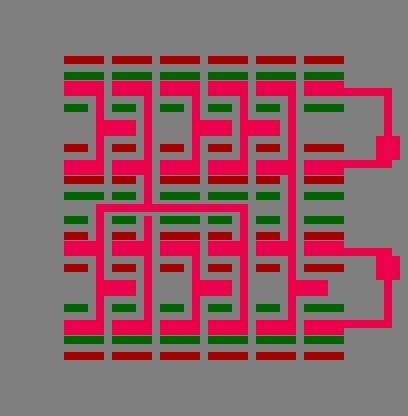

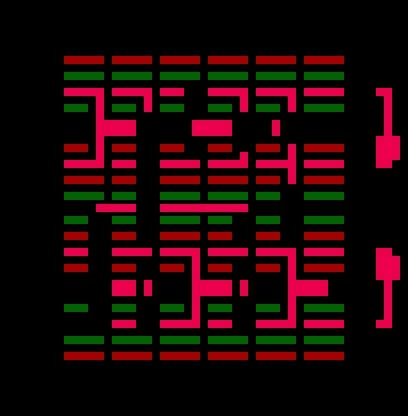

Die D-Latch-Flip-Flop-Schaltpläne

Hier sind die Schaltpläne:

Damals interessierte ich mich wirklich für das CPU-Design (und bin es immer noch), es war ein guter Anfang, aber nur knapp. Manchmal glaube ich nicht, dass es von mir entworfen wurde, als ich erst 20 war, weil alles genau an seinem Platz war, sogar mir fielen die „Substratverbindungen“ der MOSFETs auf.

Im Moment ist mir aufgefallen, dass die Ausgänge und Eingänge gepuffert sind und in normalen D.-Latches 26 MOSFETs verwendet wurden, aber ich habe 24 MOSFETs verwendet.

Wie auch immer, ein Ein-Bit-RAM benötigt 24 MOSFETs, ein Ein-Byte-RAM benötigt 24*8 und ein Ein-Kilo-Byte-RAM enthält 196608 MOSFETs.

Wenn in meinem entworfenen Flip-Flop der „clk“-Pin „0“ ist, hat der „D“-Pin keinen Einfluss auf den „Q“-Pin. Wenn „clk“ logisch „1“ ist, zeigt „Q“ die logischen Daten auf „D“.

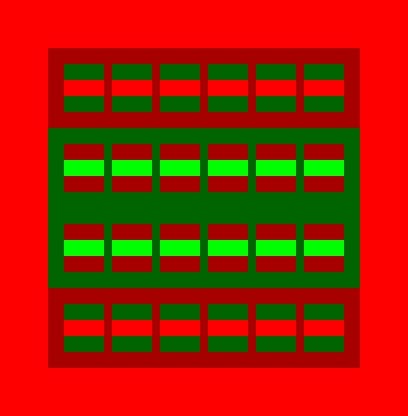

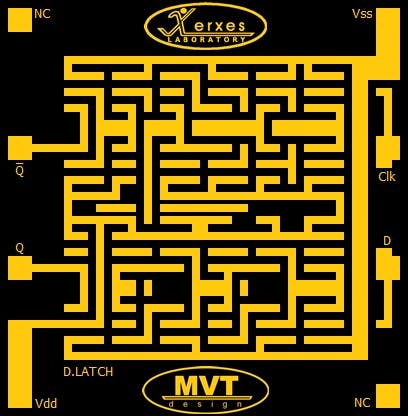

Chipschichten

Ich habe 3 Hauptschichten für den Chip in Betracht gezogen. Auf jeder Schicht müssen einige Leiterbahnen sowie P- und N-Materialien implantiert und geätzt werden.

Die erste Schicht: MOSFETs

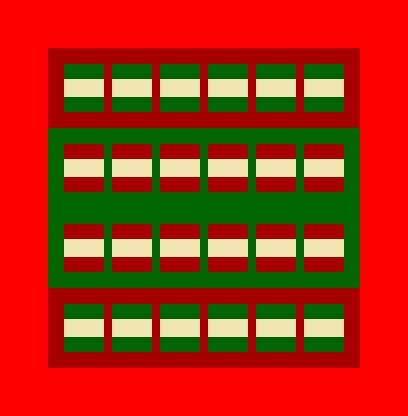

Die zweite Ebene: Untere Gleise

Die dritte Ebene: Top-Titel

Dies ist ein P-Typ-Wafer und das Hauptsubstrat für die N-Kanal-MOSFETs:

Der erste Schritt besteht darin, ein N-Typ-Substrat in den P-Typ-Wafer zu implantieren:

Der zweite Schritt besteht darin, aktive Halbleiter vom P-Typ (P+) auf dem Chip zu implantieren:

Der dritte Schritt besteht darin, aktive Halbleiter vom N-Typ (N+) auf dem Chip zu implantieren:

Der vierte Schritt ist das Ätzen der Oxide auf dem MOSFET-Gate:

Jetzt wurden 24 MOSFETs auf dem Chip implantiert.

Der fünfte Schritt besteht darin, den Chip mit einer „dielektrischen Schicht“ zu bedecken:

Der sechste Schritt ist das Ätzen einer Polyschicht (z. B. PolySi) als untere Spurschicht:

Der siebte Schritt besteht darin, die untere Schicht mit einer weiteren dielektrischen Schicht zu bedecken:

Und der achte Schritt besteht darin, die Spuren und Ein-/Ausgabepins auf dem Chip zu ätzen:

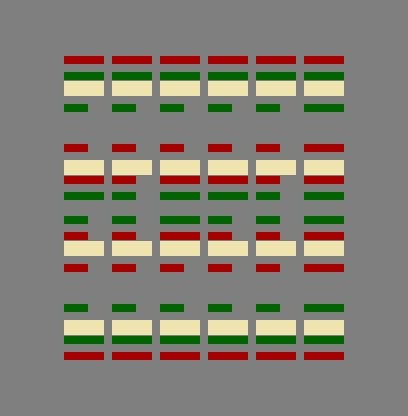

Die Prozesse

Die D-Latch-Flip-Flop-Wahrheitstabelle

// D. Latch Flip Flop True Table

// CLK| D | Q |~Q

// ---------------

// 0 | 0 | L | L

// 0 | 1 | L | L

// 1 | 0 | 0 | 1

// 1 | 1 | 1 | 0

Geschrieben von: M. Mahdi K. Kanan – Full-Stack-Elektronik- und Programmieringenieur und Gründer von WiCardTech