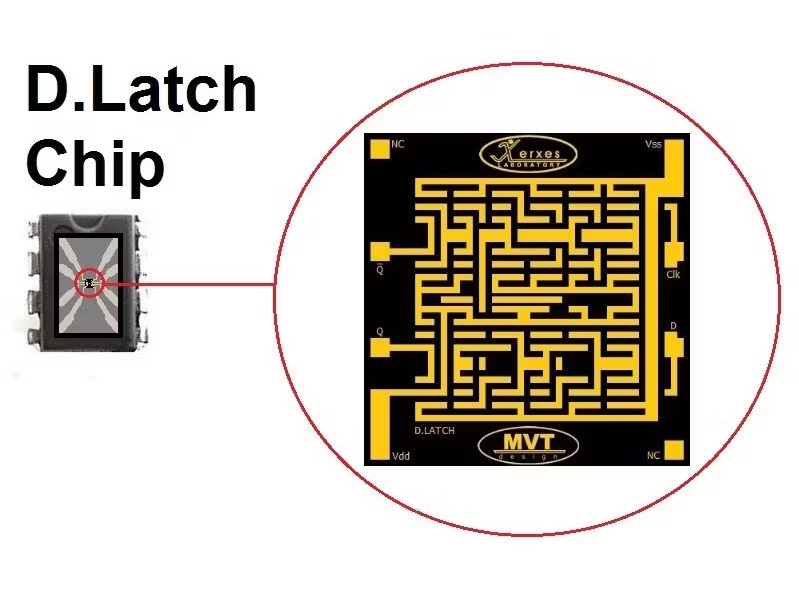

Триггер с защелкой D, дизайн микросхемы

Триггер с защелкой D (D. Latch flip-flop) на самом деле представляет собой однобитовое «оперативное запоминающее устройство (ОЗУ)». Это означает, что при запуске вывод «Q» может быть «1» или «0». Распараллелив 8 D.защелок, можно сделать 8-битное или однобайтовое ОЗУ.

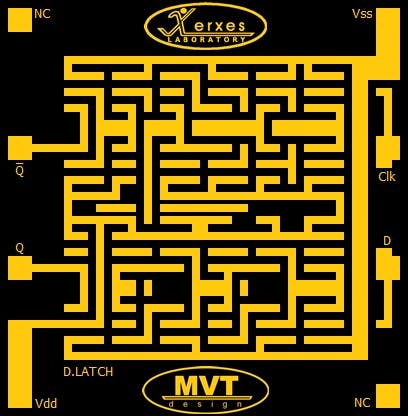

D-защелка, которую я разработал на бумаге, немного отличается от обычных схем. Когда я разработал его, мне было всего 20 лет, и я разработал его, прочитав несколько статей о цифровых вентилях и проектировании интегральных схем.

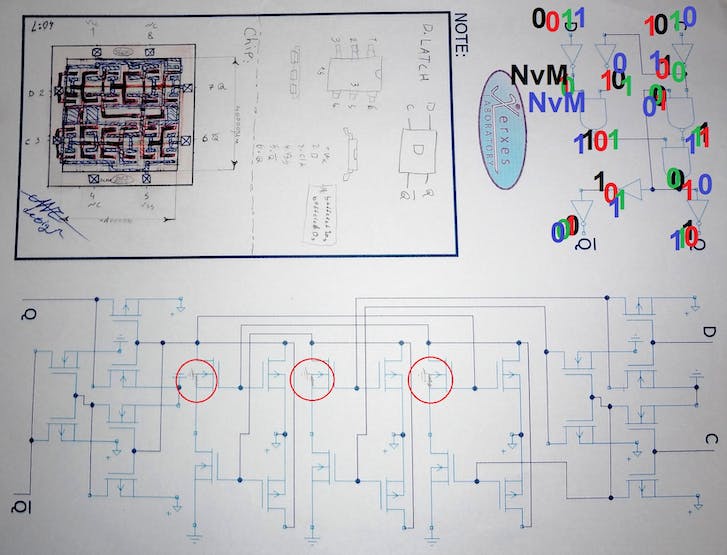

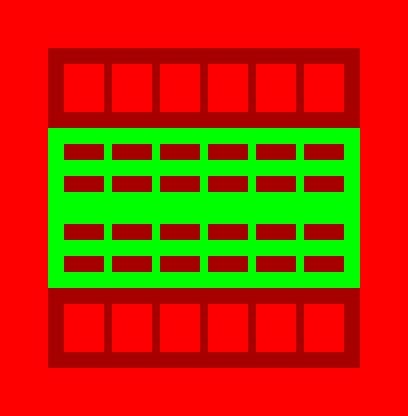

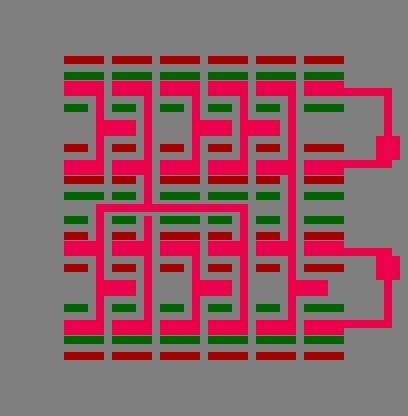

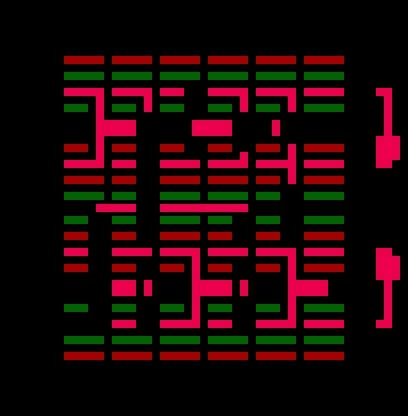

Схема триггера с защелкой D

Вот схемы:

В то время я действительно интересовался проектированием процессоров (и до сих пор интересуюсь), это было хорошее начало, но только. Иногда я не верю, что его спроектировал я, когда мне было всего 20, потому что все точно на своем месте, даже я заметил у МОП-транзисторов «подложки».

Прямо сейчас я заметил, что выходы и входы буферизованы и в обычных защелках D. используется 26 МОП-транзисторов, но я использовал 24 МОП-транзистора.

В любом случае, однобитовое ОЗУ занимает 24 МОП-транзистора, однобайтовое — 24*8, а однокилобайтовое ОЗУ содержит 196608 МОП-транзисторов.

В моем разработанном триггере, когда вывод «clk» равен «0», вывод «D» не оказывает никакого влияния на вывод «Q». Когда «clk» логически равен «1», «Q» показывает логические данные «D».

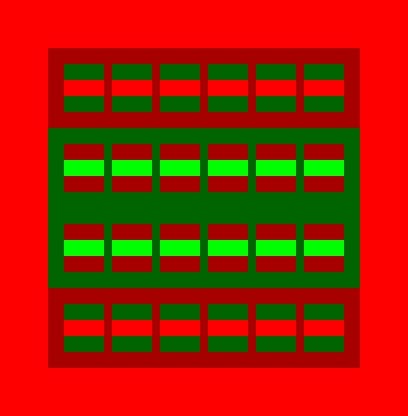

Слои чипа

Я рассмотрел 3 основных слоя чипа. На каждый слой необходимо имплантировать и вытравить несколько дорожек, а также материалы P и N.

Первый слой: МОП-транзисторы.

Второй слой: нижние гусеницы

Третий слой: лучшие треки

Это пластина P-типа и основная подложка для N-канальных МОП-транзисторов:

Первым шагом является имплантация подложки N-типа внутрь пластины P-типа:

Второй шаг — имплантация в чип активных полупроводников P-типа (P+):

Третий шаг — имплантация в чип активных полупроводников N-типа (N+):

Четвертый шаг — травление оксидов на затворе МОП-транзистора:

Теперь в чип имплантировано 24 МОП-транзистора.

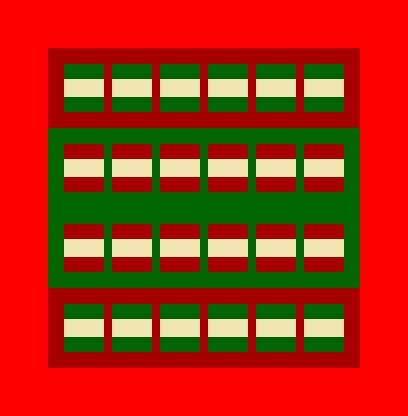

Пятый шаг — покрытие чипа «Диэлектрическим слоем»:

шестой шаг — травление слоя Poly (например, PolySi) в качестве нижнего слоя дорожки:

Седьмой шаг – покрытие нижнего слоя еще одним слоем диэлектрика:

И восьмой шаг — гравировка дорожек и контактов ввода/вывода на чипе:

Процессы

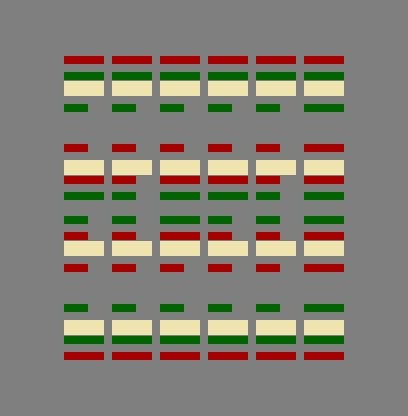

Триггер с защелкой D, Таблица истинности

// D. Latch Flip Flop Truth Table

// CLK| D | Q |~Q

// ---------------

// 0 | 0 | L | L

// 0 | 1 | L | L

// 1 | 0 | 0 | 1

// 1 | 1 | 1 | 0

Автор: М. Мahdi К. Кanan — инженер по электронике и программированию полного цикла, основатель WiCardTech