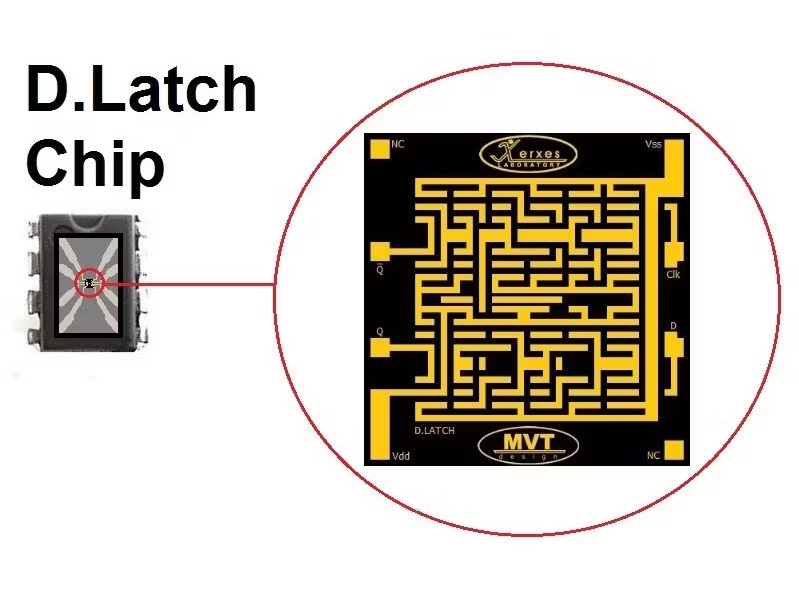

D Latch 触发器 芯片设计

D Latch 触发器 实际上是一位“随机存取存储器(RAM)”。 这意味着在启动时,“Q”引脚可能是“1”或“0”。 通过并联 8 D. Latch 触发器,您可以制作 8 位或 1 字节 RAM。

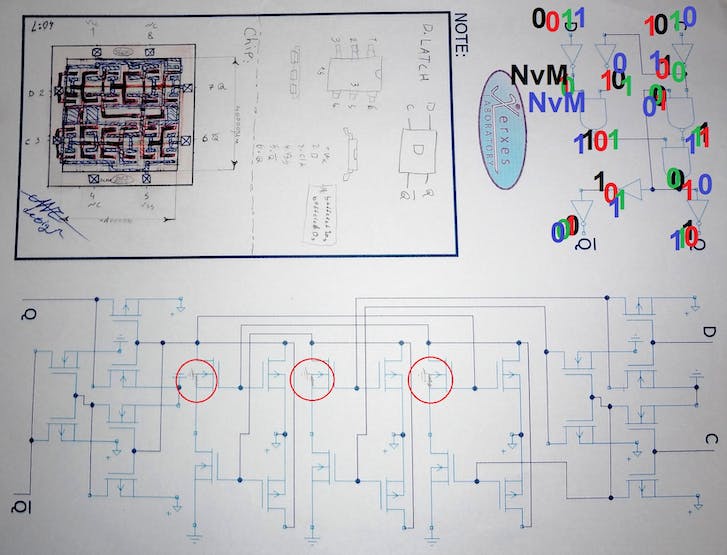

我在纸上设计的 D. Latch 触发器 与通常的原理图有点不同。 我设计的时候才20岁,是通过阅读一些关于数字门和集成电路设计的文章来设计的。

***“”电子、编程和 Arduino 项目,包括为工程师、学生和业余爱好者提供的源代码、原理图和 PCB 计划“”***

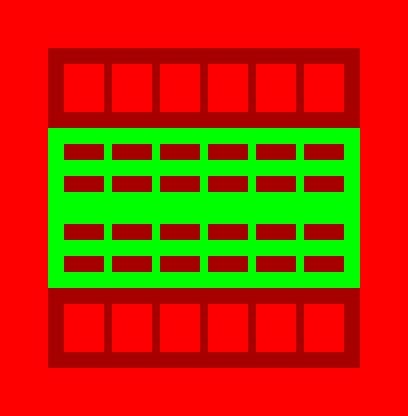

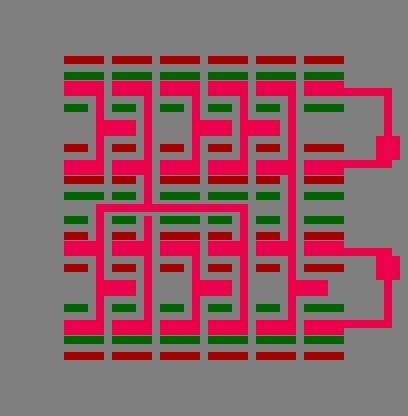

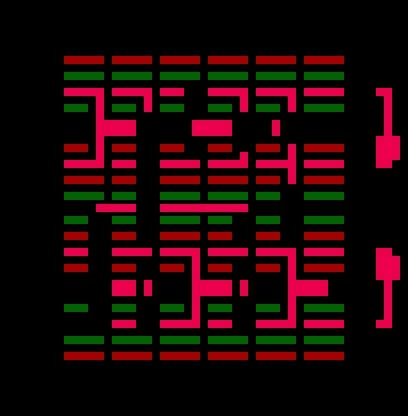

D Latch 触发器 原理图

这是原理图:

那时我对 CPU 设计非常感兴趣(现在仍然如此),这是一个良好的开始,但也仅仅是这样。 有时我不相信它是我在 20 岁时设计的,因为一切都在它的位置上,甚至我注意到 MOSFET 的“基板连接”。

现在我注意到输出和输入都经过缓冲,在通常的 D 锁存器中,它们使用 26 个 MOSFET,但我使用了 24 个 MOSFET。

不管怎样,一个1位RAM需要 24 个 MOSFET,一个字节需要24*8,一个1K字节RAM里面有196608个MOSFET。

在我设计的触发器中,当“clk”引脚为“0”时,“D”引脚对“Q”引脚没有任何影响。 当 “clk” 为逻辑“1”时,“Q”显示 “D” 上的逻辑数据。

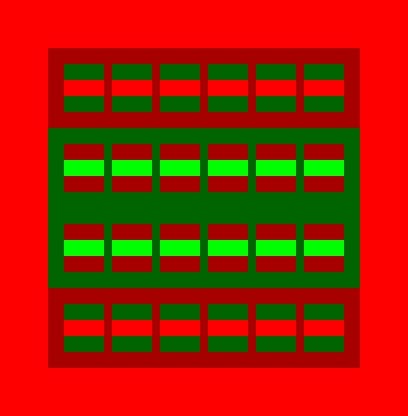

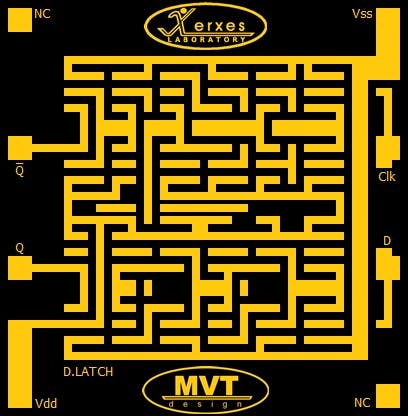

芯片层数

我考虑了芯片的 3 个主要层。 在每一层上都必须注入和蚀刻一些走线以及 P 和 N 材料。

第一层:MOSFET

第二层:底层轨道

第三层:顶级曲目

这是 P 型 晶圆 (wafer),也是 N 沟道 MOSFET 的主要基板:

第一步是将 N 型衬底植入 P 型晶圆内部:

第二步是在芯片上植入有源 P 型 (P+) 半导体:

第三步是在芯片上植入有源N型(N+)半导体:

第四步是蚀刻 MOSFET 栅极上的氧化物:

现 在,芯 片 上 已 经 植 入 了 24 个 MOSFET。

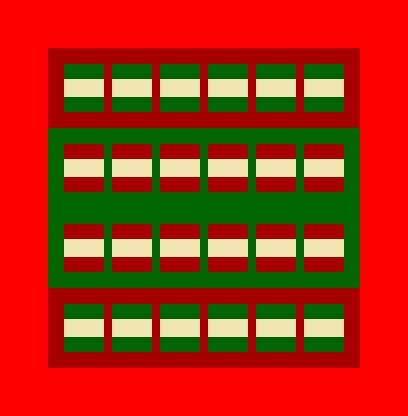

第 五 步 是 用 “介 电 层” 覆 盖 芯 片:

第六步是蚀刻多晶层(例如PolySi)作为底部走线层:

第七步是用另一个介电层覆盖底层:

第 八 步 是 在 芯 片 上 蚀 刻 走 线 和 输 入 / 输 出 引 脚:

流程

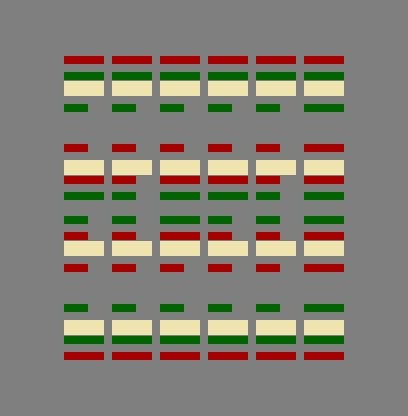

D. Latch 触发器 真值表

// D. Latch Flip Flop Truth Table

// CLK| D | Q |~Q

// ---------------

// 0 | 0 | L | L

// 0 | 1 | L | L

// 1 | 0 | 0 | 1

// 1 | 1 | 1 | 0

作者:M. Mahdi K. Kanan – 全栈电子和编程工程师、WiCardTech 创始人