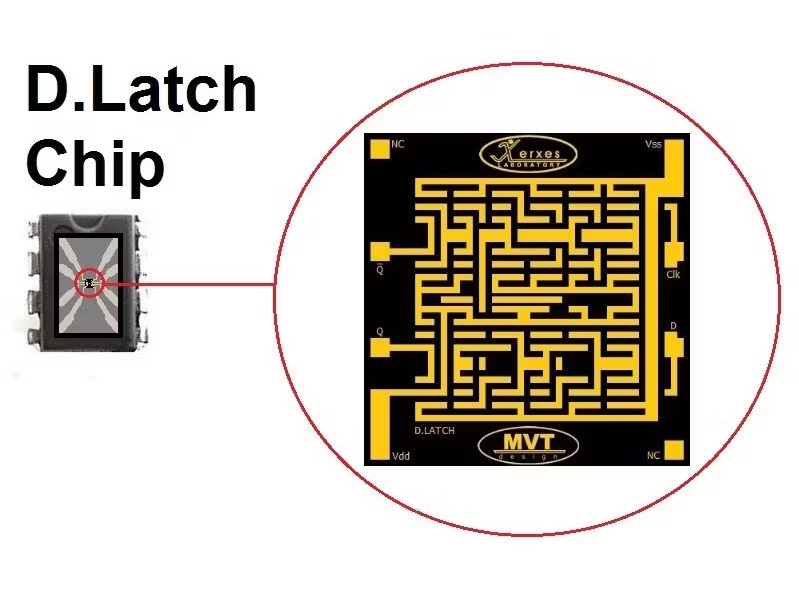

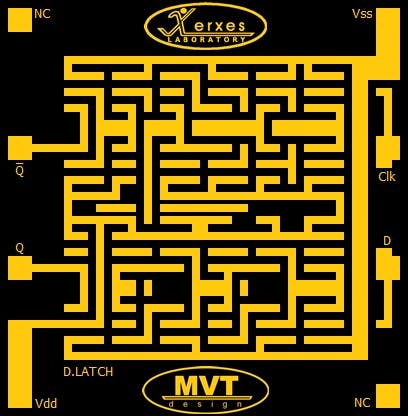

Diseño de chip flip flop con D Latch (Pestillo)

Un flip-flop D Latch es, de hecho, una «memoria de acceso aleatorio (RAM)» de un bit. Eso significa que al inicio, el pin «Q» puede ser «1» o «0». Con el paralelo 8 de D. Latches, puede crear una RAM de 8 bits o de un byte.

El D Latch que diseñé en papel es un poco diferente a los esquemas habituales. Cuando lo diseñé, tenía sólo 20 años y lo diseñé leyendo algunos artículos sobre puertas digitales y diseño de circuitos integrados.

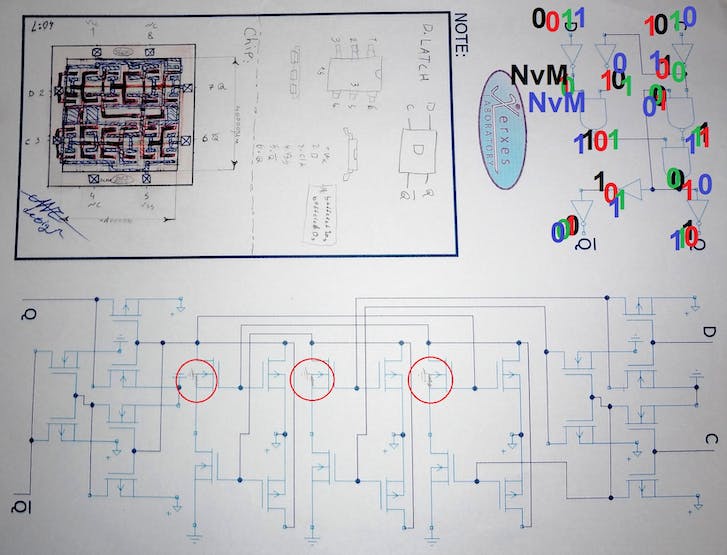

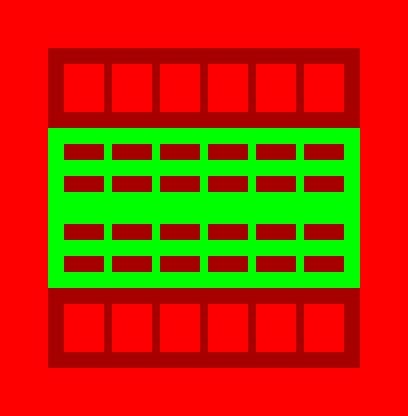

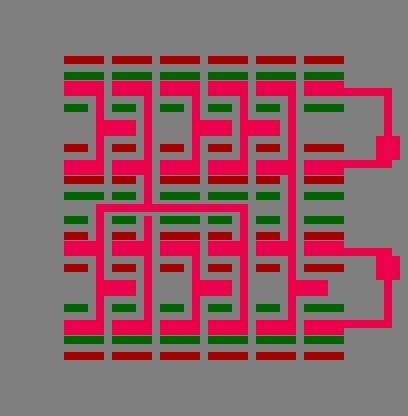

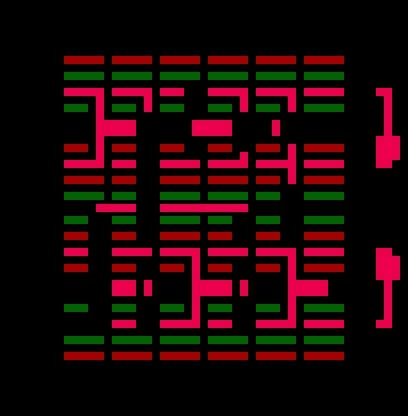

Los esquemas del flip-flop D Latch

Aquí están los esquemas:

En ese momento estaba realmente interesado en el diseño de CPU (y todavía lo estoy), fue un buen comienzo, pero por poco. A veces no creo que lo haya diseñado yo cuando tenía sólo 20 años, porque todo está exactamente en su lugar, incluso me di cuenta de las «conexiones de sustrato» de los MOSFET.

En este momento he notado que las salidas y entradas están almacenadas en el búfer y, en los pestillos D. habituales, usaban 26 MOSFET, pero yo usé 24 MOSFET.

De todos modos, una memoria RAM de un bit requiere 24 MOSFET, una memoria RAM de un byte requiere 24*8 y una memoria RAM de un kilo bytes tiene 196608 MOSFET en su interior.

En mi flip-flop diseñado, cuando el pin «clk» es «0», el pin «D» no tiene ningún efecto en el pin «Q». Cuando «clk» es lógicamente «1», la «Q» muestra los datos lógicos en «D».

Capas de virutas

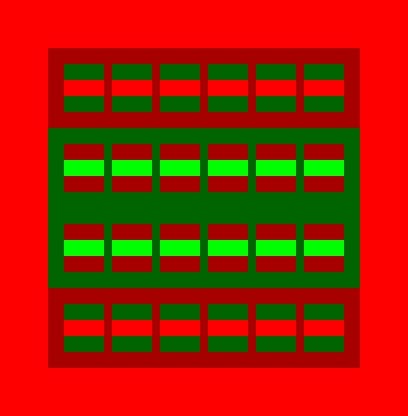

Consideré 3 capas principales para el chip. En cada capa se deben implantar y grabar algunas pistas y materiales P y N.

La primera capa: MOSFET

La segunda capa: pistas inferiores

La tercera capa: pistas principales

Esta es una oblea (Wafer) tipo P y el sustrato principal para los MOSFET de canal N:

El primer paso es implantar el sustrato tipo N dentro de la oblea tipo P:

El segundo paso es implantar semiconductores Active P-Type (P+) en el chip:

El tercer paso es implantar semiconductores Active N-Type (N+) en el chip:

El cuarto paso es grabar los óxidos en la puerta del MOSFET:

Ahora, se han implantado 24 MOSFET en el chip.

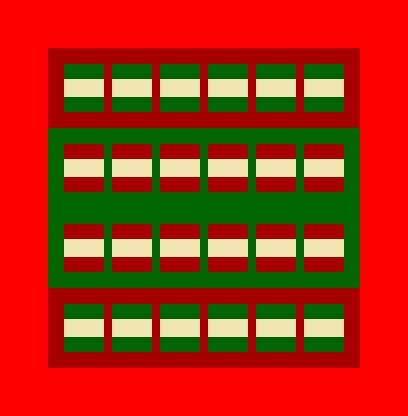

El quinto paso es cubrir el chip con una «capa dieléctrica»:

El sexto paso es grabar la capa Poly (por ejemplo, PolySi) como capa inferior de la pista:

El séptimo paso es cubrir la capa inferior con otra capa dieléctrica:

Y el octavo paso es grabar las pistas y los pines de entrada/salida en el chip:

Los procesos

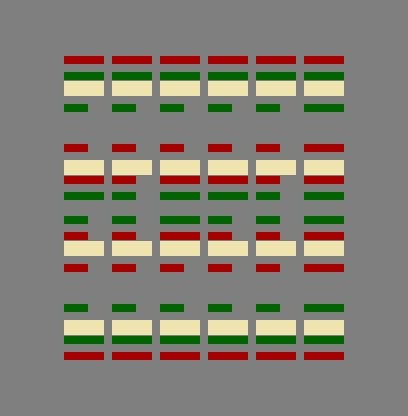

La tabla de verdad de Flip Flop D Latch

// D. Latch Flip Flop Truth Table

// CLK| D | Q |~Q

// ---------------

// 0 | 0 | L | L

// 0 | 1 | L | L

// 1 | 0 | 0 | 1

// 1 | 1 | 1 | 0

Escrito por: M. Mahdi K. Kanan – Ingeniero de programación y electrónica de pila completa y fundador de WiCardTech